8b/10b編碼

概要[Abstract]

8b/10b編碼是一種可以保證DC平衡的編碼機制,即通過這種編碼機制,8位的數(shù)據(jù)變成了10位,但是數(shù)據(jù)流中的“0”和“1”基本保持平衡。8b/10b編碼是目前許多高速串行總線中的編碼機制,如USB3.0、1934b、Serial ATA、PCI Express、Infini-band、Fibre Channel、RapidIO等總線或者網(wǎng)絡(luò)。

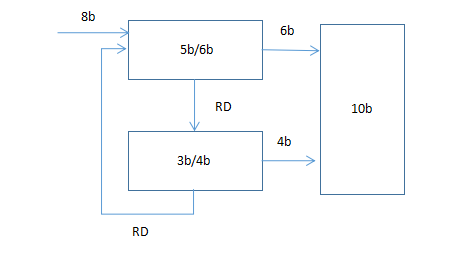

本設(shè)計中,將8b/10b轉(zhuǎn)換分為兩步實現(xiàn),第一步將低五位變成六位,第二步將高三位變?yōu)樗奈唬?/span>5b/6b轉(zhuǎn)換和3b/4b轉(zhuǎn)換。為表述方便,將八位數(shù)據(jù)HGFEDCBA記為D.x.y,其中x代表低五位EDCBA對應(yīng)的十進制數(shù),y代表高三位HGF對應(yīng)的十進制數(shù)。在轉(zhuǎn)換過程中,利用極性偏差(running disparity,RD)[注:RD只能為-1和+1]來控制數(shù)據(jù)流的DC平衡,給定初始的RD=-1(也可以為+1),在5b/6b轉(zhuǎn)換之后根據(jù)6b數(shù)據(jù)的不均等性(disparity)[注:不均等性即“1”和“0”的個數(shù)差值]來決定輸出的RD,輸出的RD值進一步?jīng)Q定3b/4b的譯碼方式,而4b數(shù)據(jù)的不均等性又決定輸出的RD值,然后輸出的RD又作為下一個8b/10b轉(zhuǎn)換的初始RD值,RD值和數(shù)據(jù)轉(zhuǎn)換的關(guān)系如下圖所示:

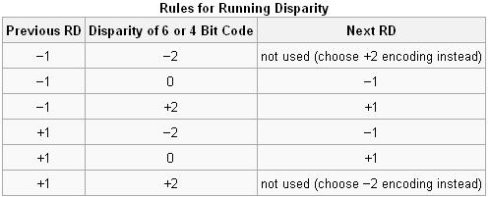

對于RD的值,按下表的規(guī)則來確定:

可以很簡單的理解該表:當6b或者4b的數(shù)據(jù)中“0”和“1”個數(shù)相等時,RD保持不變,當“0”和“1”個數(shù)不相等時,RD變值。

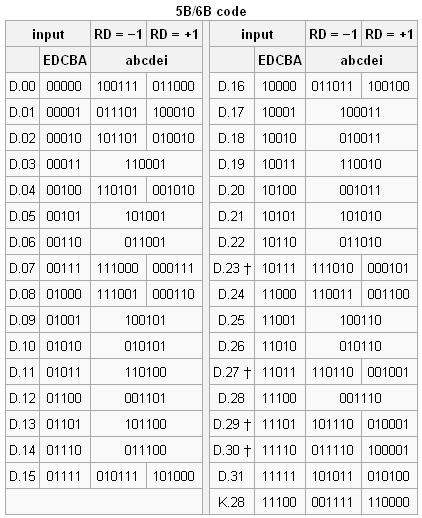

5b/6b的編碼規(guī)則如下:

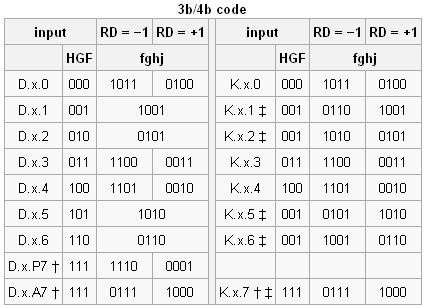

3b4b編碼的規(guī)則如下:

其中8b數(shù)據(jù)HGFEDCBA的低五位經(jīng)過5b/6b編碼將EDCBA編碼成abcdei,高三位HGF經(jīng)過3b/4b編碼成fghj,最終形成10b數(shù)據(jù)abcdeifghj.

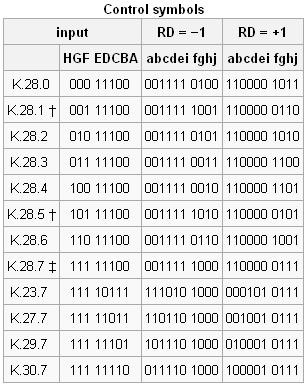

數(shù)據(jù)編碼時分為一般代碼和控制代碼,一般代碼的前綴為“D”,控制代碼的前綴為“K”,對于8b的低五位為28的數(shù)據(jù),利用K.28.y進行編碼,當x=23,27,29,30且y=7時,也利用K.x.7進行編碼,其他均按一般代碼的編碼規(guī)則編碼,即控制碼組如下:

除此之外,在一般代碼的編碼規(guī)則中,只有D.x.7的編碼情況比較特殊,分為D.x.A7和D.x.P7,D.x.A7用在當x=17,18,20且RD=-1或者當x=11,13,14且RD=+1時,其他的D.x.7全按照D.x.P7方式進行編碼。

這些不一樣的編碼方式都是為了盡量保證編碼中的“0”和“1”的平衡。

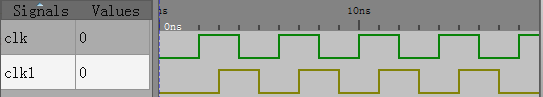

在我的設(shè)計中,利用兩個不一樣的時鐘信號觸發(fā)編碼過程,兩個時鐘信號如下:

利用兩個時鐘編碼原因是:在一個8b數(shù)據(jù)轉(zhuǎn)換中,5b/6b轉(zhuǎn)換和3b/4b轉(zhuǎn)換及輸出的RD(RD1)賦值給輸入的RD(RD2)[注:這是為了給下一個8b/10b轉(zhuǎn)換賦初始RD值]需要在不同的時刻完成(為了避免數(shù)據(jù)的競爭而出現(xiàn)錯誤)。

兩個時鐘clk和clk1均是周期為4ns的時鐘信號,只不過clk1比clk延遲了1ns,在clk的上升沿時,完成5b/6b的轉(zhuǎn)換,在clk1的上升沿時,完成3b/4b的轉(zhuǎn)換,在clk的下降沿時,完成輸出的RD1對輸入的RD2的賦值以及輸出10b數(shù)據(jù)。

在本設(shè)計中,一共分為五個小模塊:atoal(取8b數(shù)據(jù)的低五位)、atoah(取8b數(shù)據(jù)的高三位)、fivesixtransform(5b/6b轉(zhuǎn)換)、threefourtransform(3b/4b轉(zhuǎn)換)以及blbhtob(輸出10b

數(shù)據(jù)),在設(shè)計中,為了表示簡單,將RD設(shè)置成一位的數(shù)據(jù),其值有“0”和“1”,故用“0”表示RD=-1,用“1”表示RD=+1。

需要注意的是,每一個8b數(shù)據(jù)的輸入要在clk為低電平時完成,否者就會造成數(shù)據(jù)丟失。

在驗證過程中,輸入值依次取a=11110001,11101011,00011100,11111101,00000000;

預(yù)期結(jié)果分析如下:

10001(RD=-1)——100011(RD=-1),111(RD=-1)——0111(RD=+1) 輸出:1000110111

01011(RD=+1)——110100(RD=+1),111(RD=+1)——1000(RD=-1)輸出:1101001000

11100(RD=-1)——001111(RD=+1),000(RD=+1)——0100(RD=-1)輸出:0011110100

11101(RD=-1)——101110(RD=+1),111(RD=+1)——1000(RD=-1)輸出:1011101000

00000(RD=-1)——100111(RD=+1),000(RD=+1)——0100(RD=-1)輸出:1001110100

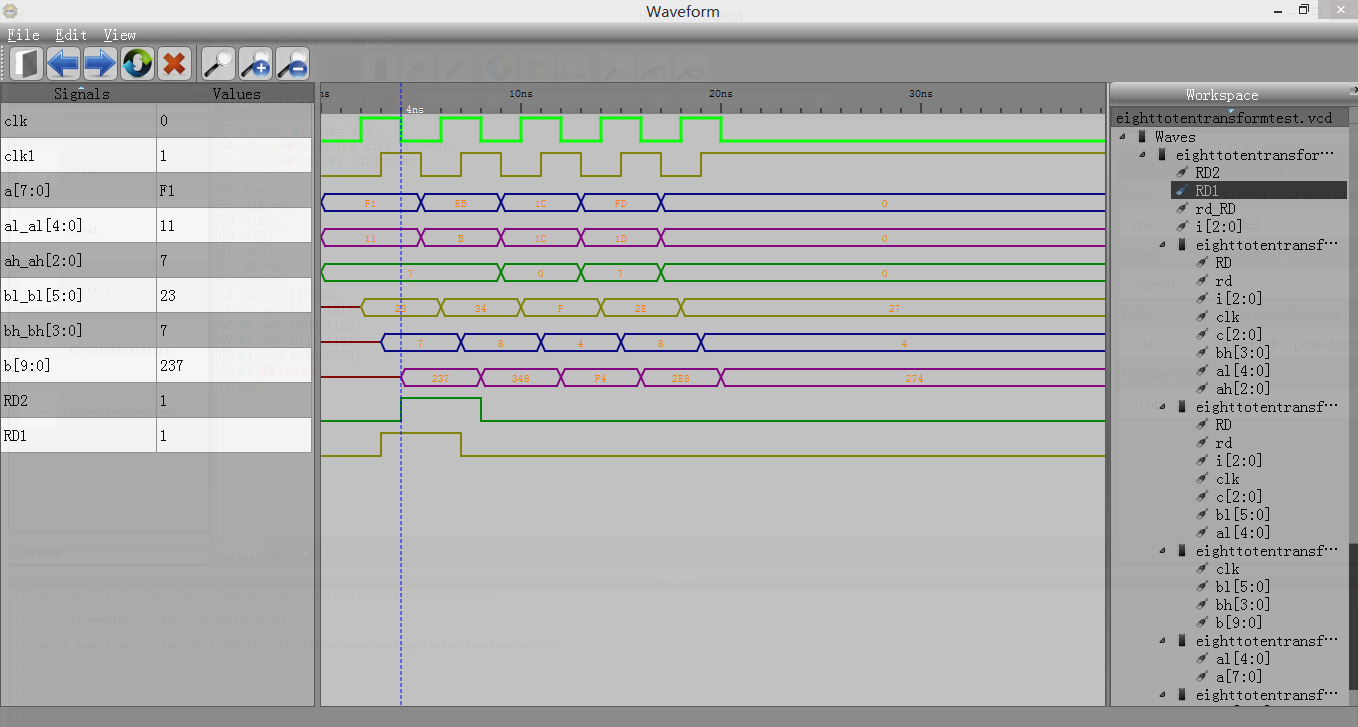

運行結(jié)果如下:

輸出結(jié)果依次為:237(1000110111)、348(1101001000)、F4(0011110100)、2E8(1011101000)、274(1001110100)

運行結(jié)果與預(yù)期分析結(jié)果一致,且6b和4b數(shù)據(jù)以及RD也與分析結(jié)果一致。

下載[Download]:design/10110.rar

TEL:+86-18562888017

TEL:+86-18562888017

Email: robei[at]robei.com

Email: robei[at]robei.com